1. 기술로드맵

□ 공정장비 국산화 및 첨단화에 대응하는 반도체 패키징 장비를 위한 중소기업 전략기술로드맵 구축

○ (중소기업 기술개발전략 1) 미세 선폭 개발 한계 대응으로 적층, 이종접합 등을 위한 TSV기술의 인터포저 및 고정밀 다층 접합 기술 개발

○ (중소기업 기술개발전략 2) 고성능 다기능화된 소자 제작을 위한 고집적 재배선 기술 개발

[ 「반도체 첨단 패키징 장비」 기술개발 로드맵 ]

2. 개요

가. 정의 및 필요성

(1) 정의

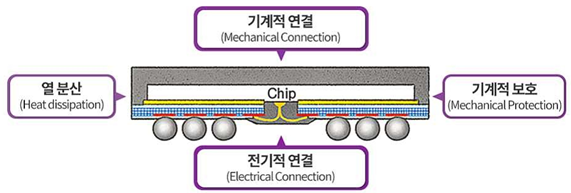

□ 반도체 패키징 장비 분야는 반도체 소자 제조 후 외부 환경으로부터 반도체 칩을 보호하고 단자 간 연결을 위한 전기적인 상호 배선, 전력 공급, 방열, 집적회로(IC)를 보호하는 일련의 장비 기술로 정의

○ 반도체 칩은 수백 단계의 웨이퍼 공정으로 메모리·로직 등의 기능을 할 수 있게 만들어졌지만, 기본적인 재료는 실리콘이므로 쉽게 깨질 위험 존재

○ 또한 웨이퍼 공정으로 형성된 구조체들은 기계적, 화학적 충격에도 취약하기 때문에 패키지 재료로 그 칩들을 보호

○ 패키지 후공정에 필요한 조립 장비들로 후면 연마, 웨이퍼 절단, 다이 접착, 선 연결, 몰드, 인쇄, 도금, 솔더 볼을 부착하는 장비들로 구성

[ 반도체 패키징 역할 ]

|

* 출처 : [반도체 후공정 2편] 반도체 패키지의 정의와 역할_SK하이닉스 뉴스룸(`22.10)

|

□ 첨단 패키징은 IC의 성능, 전력, 내구성을 높이기 위해 새로운 기술과 재료를 도입하는 것을 의미하며 미세공정 한계 극복, 고성능화 및 저전력화를 위한 첨단 패키지 기술 확보를 위한 장비 및 부품을 포함

○ 웨이퍼 레벨 패키지도 늘고 있는 추세로 대표 패키지 솔루션(FBGA, FLGA, QFN 등)이 많은 제품에 적용되고 있으며, 또 전력증폭기(PA), 프런트엔드모듈(FEM), 무선주파수(RF)· 커넥티비티 기기는 시스템 인패키지(SiP)를 사용

○ 연결성, 빅데이터 처리·고성능 컴퓨팅, 데이터 스토리지·첨단 메모리, 자동차 전장 등이 반도체 산업과 고부가가치 패키징 적용을 이끌고 있으며, 패키징 기술에는 이기종 통합과 고대역폭메모리(HBM)를 제공하는 실리콘 인터포저 등이 포함

[ 반도체장비 품목로드맵 내 반도체 패키징 장비(첨단 패키징) ]

(2) 기술개발 필요성

□ 반도체 미세공정에 따른 성능 발전 방식의 한계에 도달함에 따라 저전력·고성능 구동 조건을 충족시키는 고집적 소자 구현을 위한 패러다임 변화 요구

○ 다양한 첨단기술과 기능적 요구를 충족하기 위해 기술적으로 공정 미세화 외의 차세대 기술혁신이 촉구되며 패키징이 주목

○ 반도체 제품 성능 향상에 따라 고집적·저전력 반도체 칩을 작동시키 위한 전(前)공정 설계 기술의 패러다임을 대체하기 위한 방향으로 진화되어 패키징의 중요성이 크게 증가하는 추세

□ 메모리 초격차 지위 약화 위기, 비메모리 선도국과 격차 지속으로 반도체 전주기(설계→파운드리 제조→후공정 패키징)의 균형적 기술경쟁력 확보를 통한 경제산업적 필요성 증대

○ 2020년 OSAT 랭킹 25위 업체 중 한국은 4개 업체로 국내 OSAT기업의 시장점유율은 6% 수준, 상위 3개사가 50%의 시장 점유

□ 반도체 제품 성능 향상에 따른 반도체 패키징 공정의 중요성 증가 및 시장의 요구에 따라 필연적으로 기술력이 요구되고 있으며 산업의 고부가가치와 직결

○ 반도체 산업이 스마트폰, 자동차, 에너지, 의료, 웨어러블 디바이스 환경 등의 넓은 분야로 확산하며, 다기능 반도체에 대한 수요 증가

○ 또한 반도체 패키징 기술은 단순하게 여러 칩을 하나로 통합하는 형태에서 벗어나 동종 및 이종 기술의 융복합화를 급속히 진행하여 신시장 창출

나. 범위 및 분류

(1) 가치사슬

□ (후공정 장비/소재 밸류체인) 반도체 후공정을 살펴보면 전공정대비 상대적으로 작은 규모의 기업체들이 차지

○ 과거 후공정은 삼성전자 및 SK하이닉스가 직접 인하우스로 대부분을 진행 후 나머지 부분만 외주로 넘어온다는 인식이 강함

○ 상대적으로 업황의 등락이 심하지만, 현재는 TSV(through silicon via, 실리콘 관통 전극) 공정처럼 첨단 메모리 구동을 위해서는 후공정의 역할도 점차 커지고 있고, 외주 업체의 역할도 높아지는 추세

□ 반도체 패키지 및 조립장비 시장은 모바일기기, 전기차 등 반도체 수요가 지속적으로 확대 및 삼성전자의 패널 레벨 패키징 등 새로운 패키징 기술이 등장하면서 관련 장비 수요 증가도 함께 기대

○ 제품별로 기술력이 높은 국내외 소수 기업이 시장을 주도하고 있어 후발 기업의 시장진입은 다소 어려울 것으로 전망

[ 반도체 패키징 장비 품목 산업구조 ]

후방산업

| 반도체 패키징 장비

| 전방산업

|

전자, 기계, 광학, 소프트웨어, 부품

| Back grinder, Dicer, Bonder, Molder, Triming/Forming, Ball attacher, Singulator, Laser Marker, Cure oven, Plating

| 반도체, 컴퓨터, 휴대폰, 디지털가전,

정보통신, 자동차, 에너지 및 의료기기

|

* 출처 : 중소기업 전략기술로드맵 2023-2025 반도체·디스플레이장비_중소벤처기업부(`22)

|

(2) 용도별 분류

□ 패키징 기술 구분

○ 메모리제품의 경우 리드프레임(leadframe)과 FBGA 제품이 90% 이상을 차지하고 있으며 시스템반도체의 경우에는 반대로 SIP, Flipchip, 웨이퍼레벨(wafer level) 패키지로 구분

차세대 패키징 기술의 개발을 통해 기존 패키징 공정에서 발생하는 병목 현상을 해소하여, 전공정을 통한 IC 미세화에 의존하는 비효율적인 구조를 개선

[ 주요 패키징 유형별 특징 ]

구분

| 특징

|

(리드프레임 기반)

QFN(Quad Flat No-Lead)

TSOP(Thin Small Outline Package)

| · 와이어 본딩 후 몰딩하는 전통적인 패키징 방식으로, 작고 가벼워 전기적 성능과 열적 특성이 우수

· 리드프레임 사용 시 메모리반도체 패키징으로 사용

|

(볼 그리드 어레이)

BOC(Board On Chip)

FC(Flip Chip Package)

| · 와이어 대신 bump를 결합 소재로 사용하는 방식으로 TSOP 등 전통적인 방식에 비해 작고 얇음

· 입출력 단자 많고 전기적 특성이 좋으며 고밀도 PCB 형태로써, 메모리 패키지, TV, set top box 등에 이용

|

HI

(Heterogeneous Integration

| · 개별적으로 제조된 여러 구성 요소들(프로세서, 메모리, 센서, 광, MEMS 소자 등)을 단일 칩 크기에 준하는 수준으로 조립 및 포장

· 하나의 패키지 내의 다양한 칩을 접합하기 위해 WLP, SiP, TSV 등 기술들이 복합적으로 사용되며, 향후 고집적・다기능 소자를 구현하기 위한 주요 기술

|

이종접합 패키징

| WLP

(Wafer Level Package)

| · IC가 형성된 웨이퍼 단위로 직접 패키지 하는 형태로 PCB 기판이 불필요하여 초소형화가 가능

· 전기적 특성이 우수하며, 기존 패키징 공정 대피 원가 경쟁력이 높아 모바일 기기와 IoT 시장에서 매우 유리

|

SiP

(System in Package)

| · 서로 다른 기능의 소자들을 하나의 패키지화 하는 방식으로 소자 간 접속경로를 줄여 고성능, 우수한 전기적 특성

· 초경량. 초소형의 반도체 기능 확보하여 무선 통신 단말기 분야, MEMS, 카메라 모듈 등에 주료 활용

|

POP

(Package on Package)

| · 연결 배선 길이 최소화를 통해 모바일에서 AP, 베이스 밴드 칩과 메모리를 통합하여 초소형 부품 구현

· 모바일, PDA, 디지털카메라에서 주로 이용

|

TSV

(Through Hole Via)

| · 칩에 구멍(Via Hole) 뚫어 상・하단칩을 전극으로 연결하는 방식으로, 메모리칩을 적층하여 대용량 구현 가능

· 속도와 소비전력의 개선이 큰 폭으로 가능하여, CMOS 이미지 센서, 고용량 메모리가 필요한 제품

|

(미래 기술)

Flexible Package,

Embedded Die

| · 80μm 이하로 소자를 얇게 가공하여 플렉서블 기판에 접합하는 기술로, 휘어질 수 있어 웨어러블 제품에 적용

|

* 출처 : 반도체후공정(패키징)_KISTEP(`20.12)

|

□ 일반적으로 패키지 공정에 필요한 단위 공정 장비들로 후면 연마, 웨이퍼 절단, 다이 접착, 선 연결, 몰드, 인쇄, 도금, 솔더 볼을 부착하는 장비들이 포함

[ 공정별 분류 ]

분류

| 상세 내용

|

Back Grinding

| · 웨이퍼 뒷면을 얇게 연마하는 과정

|

Dicing and Saw

| · 칩이 형성된 웨이퍼의 칩(다이)을 개별 칩으로 분리하여 절단

|

Die Attach

| · 개별로 분리된 칩을 리드프레임(Leadframe)의 패드 또는 Substrate에 부착

|

Wire bonding

| · Au 또는 Al 선을 이용하여 칩의 전극과 Substrate를 전기적으로 연결

|

Molding

| · 칩을 외부환경으로부터 보호하기 위해 전극을 제외한 부분을 본래의 기능이 유지되도록

· 외관을 밀봉하는 과정

|

Marking

| · 패키지 표면에 반도체에 대한 제반 정보 등을 새겨 넣는 과정

|

Trim/Form

| · Lead간의 전기적 흐름을 차단하고 패키지 외부 리드 형상 제작(Normal 타입)

|

Ball attach

| · 회로가 형성된 Substrate에 솔더 볼을 부착하는 과정(BGA 타입)

|

* 출처 : 중소기업 전략기술로드맵 2023-2025 반도체·디스플레이장비_중소벤처기업부(`22)

|

3. 환경 분석

가. 시장 현황 및 전망

(1) 개황

□ 반도체 패키지는 시대에 따라 다양하게 변화되어 왔으며 기술의 발전으로 더욱 복잡하게 발전되고 있는 추세

○ 과거 1970~80년대에는 삽입실장형(Through hole mount)이 주류를 이루어 왔으나 1990년에 PCB 보드의 양면을 모두 활용할 수 있는 표면실장형(Surface mount) 패키지 형태로 발전

□ 반도체 패키징 장비 산업은 각종 공정 장비들의 대규모 설비투자를 요구하는 장치 산업으로 비교적 중소 업체들에게 진입장벽이 높은 분야

○ 반도체 패키징 및 조립 장비는 응용 분야에 따라 다양한 패키지 형태가 적용되므로 수요 기업의 요구에 맞는 제품개발이 필요

○ 반도체 패키징 및 조립 장비 산업의 특징은 진입장벽이 높은 산업, 반도체 업황에 민감한 산업, 주문제작 산업, 지식 기반 고부가가치 산업

○ 전통적인 반도체 패키징은 OSAT 기업이 주로 수행하였으나, 최근 패키지 초소형화와 그에 따른 기술적 난이도 증가에 따라 대형 파운드리와 IDM 기업이 진출

[ 반도체 패키징 장비 산업 특징 ]

특징

| 내용

|

진입장벽이 높은 산업

| · 반도체 패키징 장비는 국내외 소수 상위 기업이 시장을 선도 중이며, 기술

· 확보가 어려워 진입장벽이 높은 산업임

|

반도체 업황에 민감한 산업

| · 반도체 패키징 장비는 제품 특성상 반도체 업황에 따른 전방기업의 제품

· 생산규모에 큰 영향을 받음

|

주문 제작 산업

| · 반도체 기업 및 생산 품목에 따라 요구되는 성능 및 사양에 차이가 있기 때문에 대량생산이 어려움

|

지식 기반 고부가가치 산업

| · 기계, 전기, 전자, 재료 등 다양한 분야의 기술이 융합된 산업으로 부가가치가 높은 산업

|

* 출처 : 한국IR협의회, 기술분석보고서(`18.10)

|

□ 반도체 산업 분업화에 따른 네트워크의 중요성에 따라 패키징 장비 산업의 중요성이 증대되고 있는 추세

○ 반도체 제조산업의 기업형태는 크게 종합반도체(IDM), 팹리스, 디자인하우스, 파운드리, 패키징・테스트(OSAT)으로 구분되며 수요자 중심 산업으로 변화

○ 후공정 산업은 반도체 산업의 변화에 따라 다양한 기술을 필요로 하고 있으며, 후공정 기술의 진화가 반도체 업체 간 경쟁력 차이를 발생시키는 하나의 요인으로 작용

□ 주요국은 반도체는 국가 간 경쟁으로 주요국 경우 다양한 지원 정책으로 첨단패키지 경쟁력 확보에 주력하고 있으며 국내에서도 지원 전력 강화

○ 메모리반도체 중심의 산업구조를 탈피하기 위해 시스템반도체 경쟁력을 강화하고 생태계를 조성하기 위한 정책 추진 중이며 첨단 패키지 산업 경쟁력 강화 유도

[ 주요국 반도체 후공정(패키징) 장비 지원 정책 ]

국가

| 지원 정책

|

미국

| · 반도체과학법(칩스법) 신설, 반도체 시설투자에 25% 세액공제

· 상무부 산하에 ‘국립 첨단 패키징 제조 연구소’ 설립 및 50억 달러 규모의 인력 양성지원

· 반도체 제조 및 후공정에 200억 달러 지원을 통한 기술개발

· 미국 법안 A부 미국 반도체 기금(CHIPS for America Fund)에서 첨단 패키징 시설과 장비에 대한 예산 및 첨단 패키징 프로그램 개발 지원

|

대만

| · 국책 연구기관(ITRI) 주도로 패키지 산업 생태계 지원

· 반도체 시설투자에 25% 세액공제 및 반도체장비 구입에 5% 추가 세액공제

· 5G, AI 반도체용 3D 적층과 이종접합 기술을 발전시키기 위해 팹리스 기업에게 제품 초기 검증과 양산을 지원

|

일본

| · 후(後)공정 3D화 프로세스 기술개발 프로젝트

· TSMC社와 협력으로 3D IC 연구센터 연구소 개소 및 투자비 50% 지원

· 소부장 공급을 위해 글로벌 기업과 협업체계 구축 및 일본 소부장 업체 대만과 협력 강화

· 일본 반도체 연합 라피더스에 77억 엔 지원

|

중국

| · 첨단 패키지 기업에 세제 혜택 등으로 연구 개발 지원

· ‘중국제조 2025’계획을 발표하여 패키지 분야 3D SIP, 반도체복합구조칩, 패키징 설비 등을 중점 개발 지원으로 200억달러 및 세계 점유율 45% 달성을 목표

|

싱가포르

| · 국가 연구기관(IME) 중심으로 패키지 산업 경쟁력 확보

|

한국

| · 반도체 설비투자에 대학 대기업 세액공제를 15%, 중소기업의 경우 25% 적용

|

(2) 관련 시장 규모 및 전망

① 세계 시장

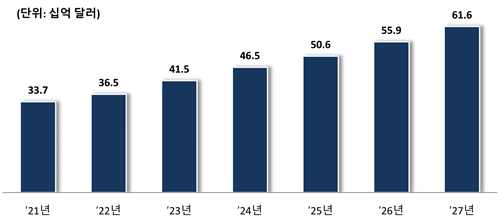

□ Yole Group은 반도체 첨단 패키징 시장이 `21~`27년 연평균 19% 성장하고, 특히 2.5D/3D 분야가 연평균 14.34% 급성장 전망

○ 초고밀도 팬아웃(UHD FO) 기술은 2027년 18.8억 달러로 가장 큰 시장 규모를 형성할 것으로 분석

□ 패키징 장비 시장은 2023년에 소폭 감소할 것으로 예상되나, 조립 및 패키징과 테스트 장비를 중심으로 성장할 것으로 전망

[ 반도체 패키징 장비 세계 시장 규모 및 전망 ]

(단위 : 십억 달러, %)

구분

| ‘21년

| ‘22년

| ‘23년

| ‘24년

| ‘25년

| ‘26년

| ‘27년

| CAGR

(‘21∼’27)

|

세계시장

| 33.7

| 36.5

| 41.5

| 46.5

| 50.6

| 55.9

| 61.6

| 10.6%

|

|

* 출처 : An OSAT Perspective On Semiconductor Market Trends_Semiconductor Engineering(`23.01)

|

② 국내 시장

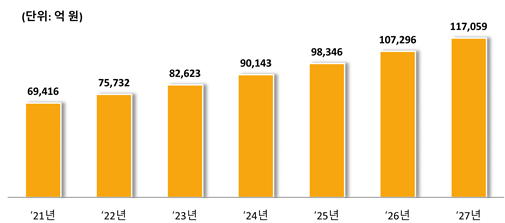

□ 2022년 7조 5,732억 원이었던 패키징 장비 국내시장 규모는 2027년 11조 7,059억 원으로 증가할 것으로 전망

○ 2014년 전세계 OSAT 업계순위 25위 안에 5개 국내 기업이 있었으나, `20년 기준 SFA, 하나마이크론, 네페스 등 3개 기업만 존재

[ 반도체 패키징 장비 국내 시장 규모 및 전망 ]

(단위 : 억 원, %)

구분

| ‘21년

| ‘22년

| ‘23년

| ‘24년

| ‘25년

| ‘26년

| ‘27년

| CAGR

(‘21∼’27)

|

국내시장

| 69,416

| 75,732

| 82,623

| 90,143

| 98,346

| 107,296

| 117,059

| 9.1%

|

|

* 출처 : 중소기업 전략기술로드맵 2023-2025 반도체·디스플레이장비_중소벤처기업부(`22)

|

나. 기술개발 동향

(1) 개황

□ (기술수준) 첨단 패키지 주요 기술의 경쟁력은 선진사와 비교하여 매우 취약하며 패키지를 포함한 후공정 산업의 점유율은 하락세

○ 삼성전자는 3나노 미세공정 파운드리에서 TSMC社보다도 먼저 양산에 성공하였지만 첨단패키징 분야/기술별 소‧부‧장 전체 Gap 분석 시, 선진사 대비 기술경쟁력 확보가 절실히 필요한 상황

□ (반도체 패키징) 반도체 초격차 경쟁력 향상을 위한 미세공정 한계 극복, 고성능화 및 저전력화를 위한 첨단 패키지 기술 확보 추세

○ 과거에는 외부 환경으로부터의 보호와 기계적 서포트가 주 목적이었다면, 현재는 점차 저항을 최소화하는 상호 접속 기능과 퍼포먼스 향상을 위한 열 관리 능력, 패키지 통합기능 등 반도체 기능을 극대화하는 역할이 점차 강조되는 추세

□ (적층) 인터포저를 사용하는 2.5D, TSV 방법으로 칩을 쌓아 올리는 3D 형태의 적층 구조가 패키징 핵심기술

○ 반도체 집적도를 향상시키기 위하여 TSMC, 삼성, 인텔 등에서 미세회로(수 nm) 반도체 개발에 힘을 쏟고 있으나, 현재 2nm 이하의 미세 선폭 개발 속도는 점차 더뎌지며 천문학적인 비용 부담으로 점차 한계에 직면하고 있는 상황

□ (이종접합) 기존 단일 칩의 성능 한계 및 높은 비용을 극복하기 위하여 개별적으로 제조된 여러 구성 요소들(프로세서, 메모리, 센서, 광, MEMS, 소자 등)을 하나의 패키지 안에 구현하는 핵심기술

○ 이종접합은 다양한 칩을 접합함으로써 향후 고집적·다기능 소자를 구현하기 위한 주요 기술이며, SiP, WLP, 3D, TSV 등 다양한 기술들이 복합적으로 사용

○ 전기적, 열적 성능이 우수하면서 작은 폼펙터로 다기능 구현이 가능한 패키지 기술로 많은 구성 요소별 연결을 위한 접합 기술개발과 제조사 및 선폭이 상이한 이종칩을 결합하는 칩렛 기술 중요

○ 또한, 미래 기술은 소자를 얇게 가공하여 플렉서블 기판에 접합하는 기술로 웨어러블 제품에 적용

○ 현재 주로 사용되고 있는 접합 소재인 범프의 사이즈는 약 30~50㎛ 수준이며 향후 초격차를 위하여 1㎛ 이하인 접합 기술개발이 필요

○ 중점기술은 마이크로 범프 접합 기술 (IMS(injection molded solder), hybrid bonding 등), 범프리스 접합 기술, 방열기술, 이종접합 장비 등

□ (재배선) 최근 반도체 패키징은 고성능 다기능화된 소자 제작으로 인한 I/O(input/output) 수 증가와 작아진 폼 팩터(form factor)를 만족시킬 수 있는 패키징 기술인 재배선의 기술개발 필요

○ 다수의 I/O 수 및 복잡한 배선은 신호지연으로 인한 성능이 저하되는 문제를 발생시켜 패키징 배선 기술개발을 통한 성능향상의 필요성이 증가하여 System-in-Packaging (SiP) 또는 원칩 기술이 발전

○ WLP 패키지의 경우 웨이퍼에 칩을 직접 형성하는 방법으로 공정 시간 단축 뿐만 아니라 가격 절감 및 방열 효과 개선으로 가장 유망한 기술

○ 최근 2.5D, 3D 및 이종접합과 같은 첨단 패키징 기술 구현 방식의 등장으로 2016년 이후 업계는 더 얇은 인터커넥트와 칩 영역 외부에서까지 재배선할 수 있는 WLP(FO-WLP)에 대한 기술개발을 본격적으로 진행

○ FO-WLP를 사용하여 인터포저가 없는 2.5D를 개발하였으며, 다양한 형태(Package on Package 등)의 얇고 고성능 3D 소자 제작 가능

○ 중점기술은 증가하는 I/O 수와 다층의 구조로 인하여 복잡한 구조에서의 최적의 배선 설계 (배선 길이, 사이즈, 구조 등) 등

(2) 주요 기술개발 동향

① 해외 기업

○ (TSMC, 대만) Wafer level chip scale package(WLCSP), Chip-on-Wafer-on-Substrate, Integrated FO 등과 같은 첨단 패키징 기술을 세계 최고 수준으로 서비스 제공

○ (ASE, 대만) `03년 이후 `17년간 전세계 1위를 한 대만의 OSAT 기업으로 글로벌 파운드리 기업과 전략적 파트너를 구축하고 패키지에서 테스트까지 독립적인 서비스를 제공

○ (Amkor, 미국) 미국의 반도체 제품 포장 및 테스트 서비스를 제공하는 글로벌 후공정 시장 세계 2위 기업

○ (JCET, 중국) 중국의 OSAT 기업으로 패키지 패러다임의 변화에 대응하여 웨이퍼 레벨 패키지, 플립 칩 인터커넥트 및 TSV 등 차별화된 솔루션 개발을 위해 노력 중

○ (ASM Pacific Technology(ASMPT), 싱가포르) 전 세계 반도체장비 시장에서 조립 및 패키징 장비 부문 시장점유율 1위를 차지

○ (Applied Materials, 미국) 반도체장비 분야 선두 기업

○ (Tokyo Electron, 일본) 일본 1위의 반도체장비업체로 최근 3D NAND 빅사이클에 의해 매출 급증

② 국내 기업

○ (삼성전자) 삼성전자는 차세대 패키지 20억 불 투자계획으로 ‘테스트&패키지(TP)센터’ 신설

○ (하나마이크론) FCBGA(Flip-chip ball grid array), 플랙서블 패키지 등 차세대 패키징 기술 개발과 함께 제품 맞춤형 최적화 패키지 기술을 적용하는 서비스 제공

○ (네패스) Wafer Level Package(웨이퍼 레벨 패키지) 기술을 기반으로 반도체의 초소형·초박형·다기능 구현이 가능한 Fan-Out Wafer Level Package를 국내 최초로 개발 및 양산에 성공

③ 국내 연구개발 기관

□ 한국기계연구원

○ 유연 기판 기반 패키징 공정 기술개발

- Height/Pitch: ≥15m/≥20m, 접촉각: ≥150°, 수분 투과율: ≤10-2g/m2/day

□ 전자부품연구원

○ 웨이퍼레벨 적층금속 접합 패키징 공정 기술 개발을 위해 필요로 하는 패터닝 공정과 금속 적층을 위한 시험 공정을 위한 증착 설비 개발

□ 한국전자통신연구원

○ 반도체 개발에 필요한 인프라 (설계환경/검증, IP,시험, 창업보육 등) 구축 및 시제품 제작(칩 제작 등)에 많은 비용이 소요되므로 정책적 지원을 통해 시스템반도체 개발에 필요한 인프라를 구축하여 공동으로 활용할 수 있도록 지원하여 시스템반도체 산업을 육성

□ 나노종합기술원

○ IoT용 센서가 요구하는 저가격, 초소형, 다기능 성능을 가지는 융복합 센서 개발을 위해 고집적 다차원 배선 공정 개발 및 응용제품 개발

□ 성균관대학교

○ 우주항공 환경에서 작동을 보장하는 반도체 패키징 핵심기술 확보를 위한 전반적 산업 동향 및 소재,공정 분야의 기술 및 현황 분석을 통한 기술개발 추진전략 기획 및 자문단 운영

□ 한국과학기술원

○ 헤테로지니어스 반도체 고단차 패키징의 고속 대면적 3D 검사기술 개발

4. 특허 분석

□ 전략품목에 대한 특허동향 분석, 기술동향 분석, 주요 출원인 분석을 통해 아래와 같이 결과 확인

[ 특허 분석 결과 ]

구분

| 분석 내용

|

특허동향 분석

| 특허증가율 분석

| 미국이 60%의 출원비중을 차지하고 있어 최대 출원국으로 반도체 첨단 패키징 장비 산업분야를 리드하고 있는 것으로 나타났으며, 다음으로 한국 18%, 일본 14%, 유럽 8% 순으로 나타남

|

기술주기 분석

| 반도체 첨단 패키징 장비 분야의 기술 위치를 살펴본 결과, 전체적인 동향은 기술혁신의 주체인 특허출원인수와 기술혁신의 결과인 특허출원건수가 꾸준히 감소하다가 최근 구간에서 증가추세로 전환되는 동향이 나타나고 있어 회복기 단계로 분석됨

|

특허영향력 분석

| 반도체 첨단 패키징 장비 품목에 대한 주요 출원인들의 경쟁력 분석 결과, 전체국가에서는 ADV CHIP ENG TECH 특허가 상업적 가치가 높은 것으로 평가됨

한국에서는 삼성전자의 특허가 질적수준이 가장 높고 삼성전자, 엘지이노텍의 기술영향력/시장확보력이 상대적으로 모두 높은 것으로 분석됨

|

기술동향 분석

| 기술개발동향 변화분석

| 반도체 첨단 패키징 장비 품목 분석 결과, 반도체 패키지 키워드가 주로 도출되었으며, 반도체 첨단 패키징을 위한 ‘Wafer Level’ 및 ‘Electrically Connected’ 키워드가 도출된 것으로 조사됨

|

기술현황 분석

| 반도체 첨단 패키징 장비 품목은 섹션 H 전기(67%), 섹션 G 물리학 기술분야의 비중(26%)이 높은 것으로 나타났으며, 그중에서도 반도체 장치(H01L), 전기에 의한 디지털 데이터처리(G06F) 분야에서 집중적으로 연구가 진행되고 있는 것으로 분석됨

|

기술집중력 분석

| 반도체 첨단 패키징 장비 관련 기술에 대한 HHI(허핀달-허쉬만)지수 분석결과, 전체 184로 경쟁적인 시장이 형성되어 있으므로 시장진입이 다소 용이한 것으로 분석됨

|

주요 출원인 분석

| 출원인 동향 분석

| 반도체 첨단 패키징 장비 품목의 주요 출원인을 살펴보면, 주요 국가별 출원인이 고르게 포함되어 있는 것으로 나타났으며 제 1출원인은 미국의 INTEL인 것으로 조사됨

|

주요 출원인 기술 키워드 및 주요 특허 분석

| INTEL는 Semiconductor Package, Package Substrate 등의 키워드가 도출되었으며. 적층 반도체 패키지 기술력이 높은 것으로 조사됨

삼성전자는 Semiconductor Chip 등의 키워드가 도출되었으며, 칩 온 칩 반도체 패키지 기술력이 높은 것으로 조사됨

MICRON TECH는 Bond Pad, Semiconductor Wafer 등의 키워드가 도출되었으며, 멀티 칩 웨이퍼 레벨 패키지 기술력이 높은 것으로 조사됨

|

□ 4개 평가지표(활동도, 부상도, 시장력, 영향력)에 따른 정량적 분석 결과는 아래와 같이 도출

[ 평가지표/ 정량적 분석 ]

평가지표

| 한국

| 미국

| 유럽

| 일본

|

전체

| 중소기업

|

특허 활동도

| 42.6

| 18.5

| 100.0

| 9.5

| 30.3

|

특허 부상도

| 78.7

| 92.0

| 71.6

| 100.0

| 23.1

|

특허 시장력

| 54.7

| 36.4

| 100.0

| 93.7

| 65.7

|

특허 영향력

| 31.6

| 16.3

| 100.0

| 80.8

| 65.1

|

|

상대적 기술경쟁력

| 55.9

| 43.9

| 100.0

| 76.4

| 49.6

|

*각 평가지표 값은 원 계산 값에 상대적 비교의 편의성을 위해 최고점 100점으로 환산한 값이며, 상대적 기술경쟁력은 각 평가지표의 가중치를 1:1로 반영하여 평균값을 도출한 것임

[ 주요 특허 선별지표 ]

선별지표

| 가중치

|

패밀리 특허 수(A)

| 2

|

피인용 횟수(B)

| 2

|

발명자 수(C)

| 2

|

청구항 수(D)

| 1.5

|

등록 여부(E)

| 1.5

|

IPC 수(F)

| 1

|

|

선별지표 최종 계산식

| (A+B+C)X2 + (D+E)X1.5 + (F)X1

|

5. 기술개발 로드맵

□ 전략품목에 대한 핵심기술 및 개발목표 등을 토대로 기술개발 로드맵 구축

[ 「반도체 패키징 장비(첨단 패키징)」 기술개발 로드맵 ]

중분류

| 핵심기술

| 기술

요구사항

| 개발목표

| 최종목표

|

1차년도

| 2차년도

| 3차년도

|

공정장비

(부

품)

국산화

및

첨단화

| TSV 인터포저 활용 3차원 적층 기술

| · Si interposer 및 메모리 소자 등 다양한 형태의 수직배선 공정 확보

· Cu bonding pad 형성을 위한 CMP공정 기술 개발

| · 고밀도 Si 브릿지 내장 인터포저 제조기술 개발

· 고밀도 가능한 내장 인터포저 소재 선정 및 평가

| · TSV의 고주파 특성 및 signal model 개발

· 2.3D향 수동소자 내장형 유기 인터포저 제조기술

· Si interposer 및 메모리 소자 등 다양한 형태의 수직배선 공정 기술

| · TSV 적용 On Board Type Module Package기술개발 (시제품 제작)

· Cu bonding pad 형성을 위한 CMP공정 기술

· Glass 인터포저향 through-glass via(TGV)가공 및 Via-Filling 공정 개발

| · TSV 인터포저를 이용한 3D적층 패키징기술 개발

· 내장 인터포저 소재 선정 및 제조 기술

· Si interposer 및 메모리 소자 등 다양한 형태의 수직배선 공정 기술

· Cu bonding pad 형성을 위한 CMP공정 기술

|

고정밀 다층 접합 기술

| · 선도기업(TSMC, Intel, Apple)의 기술과 동등 혹은 그이상 수준의 이종집적기술 개발

· Chiplet기술 관련 독보적 특허 획득 및 공정 장비 개발

| · 피치 45㎛급 열압착접합/MuF) 55㎛급 Reflow & MuF 구현 가능한 Chip to Wafer 접합 기술개발

· Chip to Wafer Bond 최소 Pitch 구현을 위한 소재 및 공정 기술 개발

· 디바이스별의 열적 특성과 관계없이 열손상 방지 및 접합 정밀도 향상을 위한 공정 기술

· 접합 공정 양산 가능한 CoW bonding 공정 장비 설계

| · 피치 35㎛급 다층 접합, 피치 30㎛급 chiplet integration 구현 가능한 Chip to Wafer 접합 기술 및 소재/공정 기술 개발

· 접합 공정 양산 가능한 CoW bonding 공정 장비 제작

| · 피치 25㎛급 다층 접합, 피치 20 ㎛급 chiplet integration 구현 가능한 Chip to Wafer 접합 기술개발

· 솔더의 용융점이상에서 최소 유지 시간 및 불량 최소화 접합 공정 개발

· 접합 공정 양산성 1,000 UPH 이상의 CoW bonding 공정 장비 개선 및 성능 평가

| · 인터커넥션 피치 축소와 그에 따른 정밀도 향상 공정 기술

· CoW bonding장비 개발

|

고집적 재배선 기술

| · 국내 OSAT 및 IDM 업체들의 사업화 및 기술 고도화를 위해 소재 국산화 및 공정기술 개발

· 대면적 warpage 제어가 가능한 몰딩 소재 국산화 및 공정 개발

| · 재배선 선폭 10μm, 범프 피치 55μm, 50 ㎛급 warpage를 지닌 다층 재배선 구조의 배선공정 기술

· 저온 고속 몰딩 장비 설계

· 전기적 신뢰성 평가

· 기계적 신뢰성 평가

| · 재배선 선폭 2 μm, 범프 피치 50 μm, 15㎛급 warpage를 지닌 층수 증가 및 재배선 기판의 고밀화를 위한 다층 재배선 구조의 배선공정 기술

· 미세패턴 RLD용 PID 기술

· 저온 고속 몰딩 장비 제작 및 평가

· 전기적 신뢰성 및 기계적 신뢰성 평가

| · 재배선 선폭 1 μm, 범프 피치 30 μm, 12 ㎛급 warpage를 지닌 다층 재배선 구조의 배선공정 기술

· 저온 고속 몰딩 장비 성능 평가 및 최적화

· 전기적 신뢰성 및 기계적 신뢰성 평가

| · 층수 증가 및 재배선 기판의 고밀화

· 미세패턴 RDL용 PID 개발

· 저온 고속 몰딩 장비 개발

|